|

I am a master student advised by Prof. Jun Tao at Fudan University, where I received my B.S. degree. I am very lucky to work with Prof. Zhiru Zhang on ML for EDA at Cornell University, Prof. Yiyu Shi on Federated Contrastive Learning at the University of Notre Dame, and Prof. Peng Li on statsitical model for EDA at University of California, Santa Barbara. (chronically) My research interest is at the intersection of machine learning and system/hardware design. |

|

|

|

|

|

|

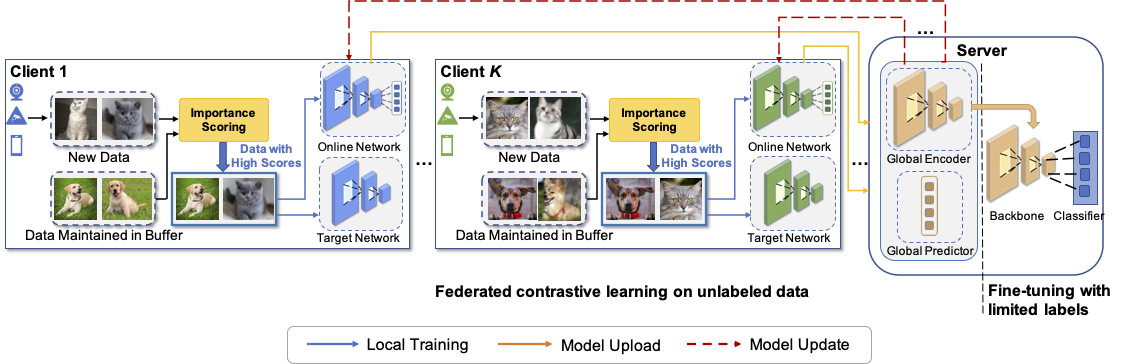

Jiahe Shi, Yawen Wu, Dewen Zeng, Jun Tao, Jingtong Hu, Yiyu Shi IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), 2023 [paper] The first work that enables learning visual representations from unlabeled streaming data on resource-restricted distributed devices. |

|

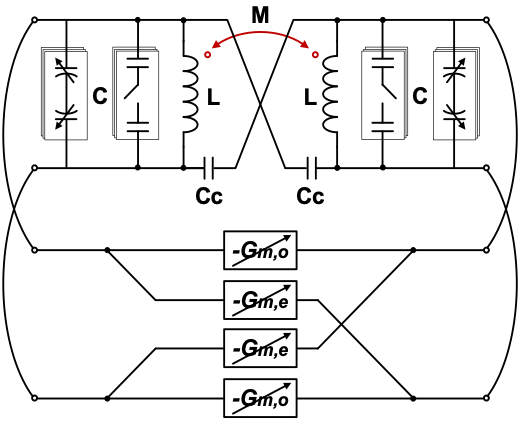

Yizhuo Wang, Jiahe Shi, Hao Xu, Shujiang Ji, Yiyun Mao, Tenghao Zou, Jun Tao, Hao Min, Na Yan IEEE Journal of Solid-State Circuits (JSSC), 2023 [paper] [bibtex] Developed an algorithm to automatically optimize the capacitor array in a wideband VCO. |

|

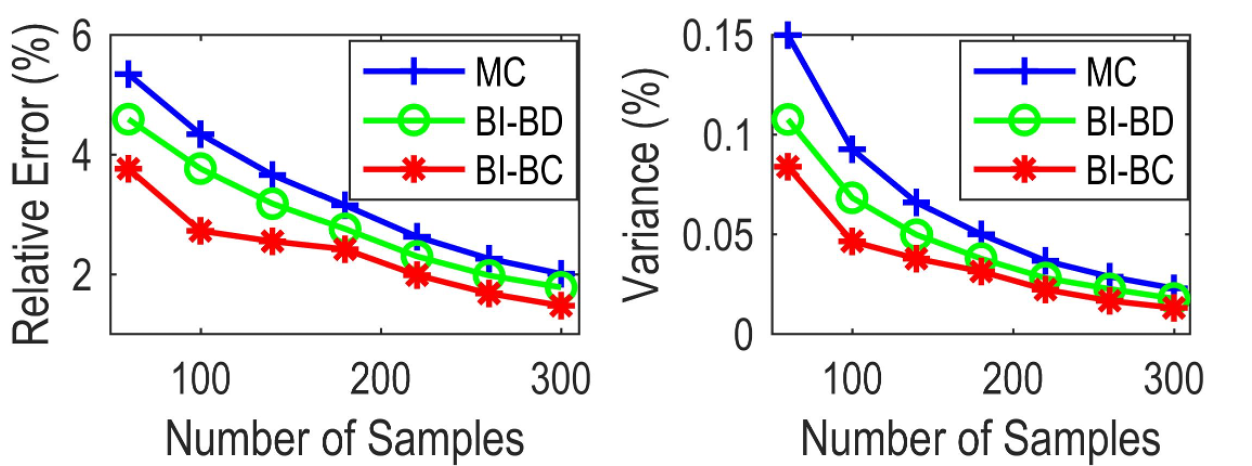

Jiahe Shi, Zhengqi Gao, Jun Tao, Yangfeng Su, Dian Zhou, Xuan Zeng IEEE International Symposium on Circuits and Systems (ISCAS), 2020 [paper] [bibtex] A novel Bayesian Inference method based on Bernoulli distribution with conjugate prior to efficiently estimate parametric yields over multiple PVT corners. |

|

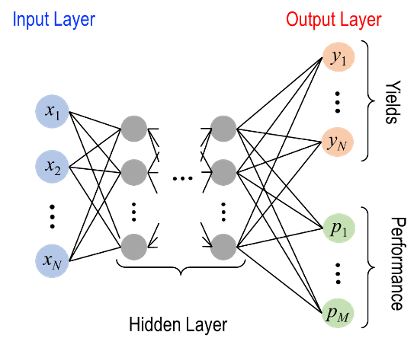

Nanlin Guo, Fulin Peng, Jiahe Shi, Fan Yang, Jun Tao, and Xuan Zeng ACM Transactions on Design Automation Electronic System (TODAES), 2023 [paper] [bibtex] An efficient Bayesian optimization method based on Bayesian neural network for yield optimization in multiple environmental corners. |

|

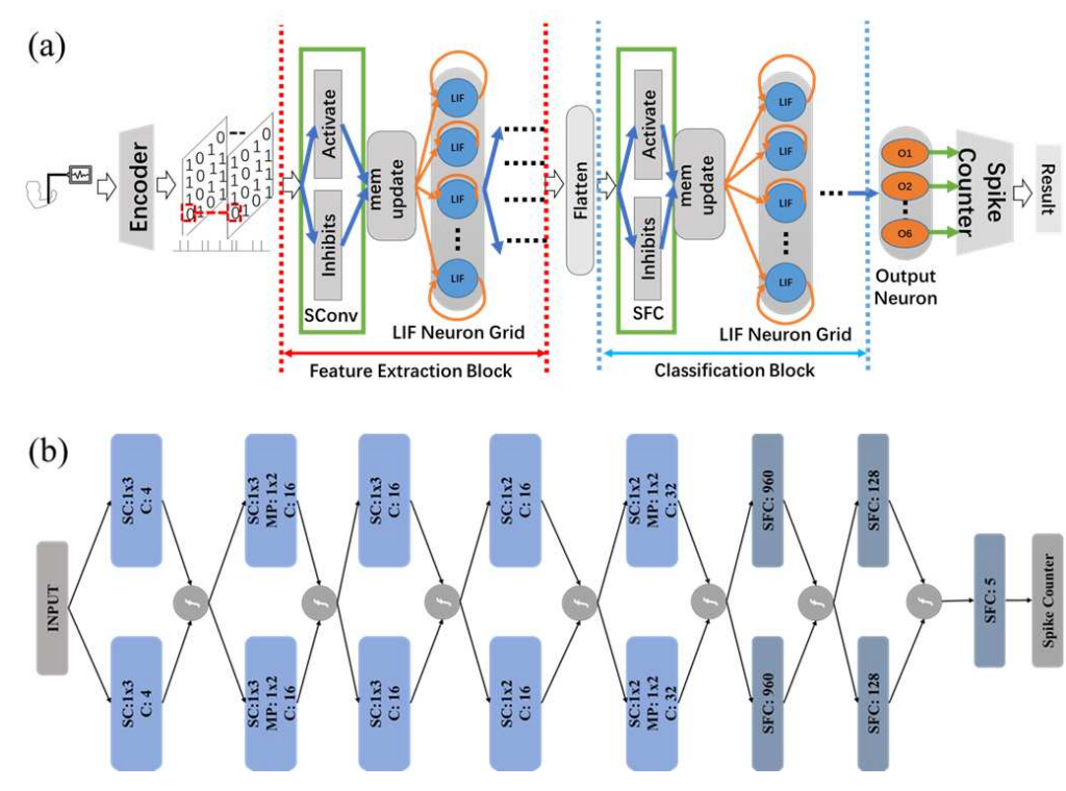

Fengshi Tian, Jingwen Jiang, Jinhao Liang, Zhiyuan Zhang, Jiahe Shi, Chaoming Fang, Hui Wu, Xiaoyong Xue, Xiaoyang Zeng IEEE International Symposium on Circuits and Systems (ISCAS), 2022 [paper] [bibtex] A new neuromorphic learning and computing approach for electromyogram (EMG) based hand gesture recognition tasks. |

|

|

|

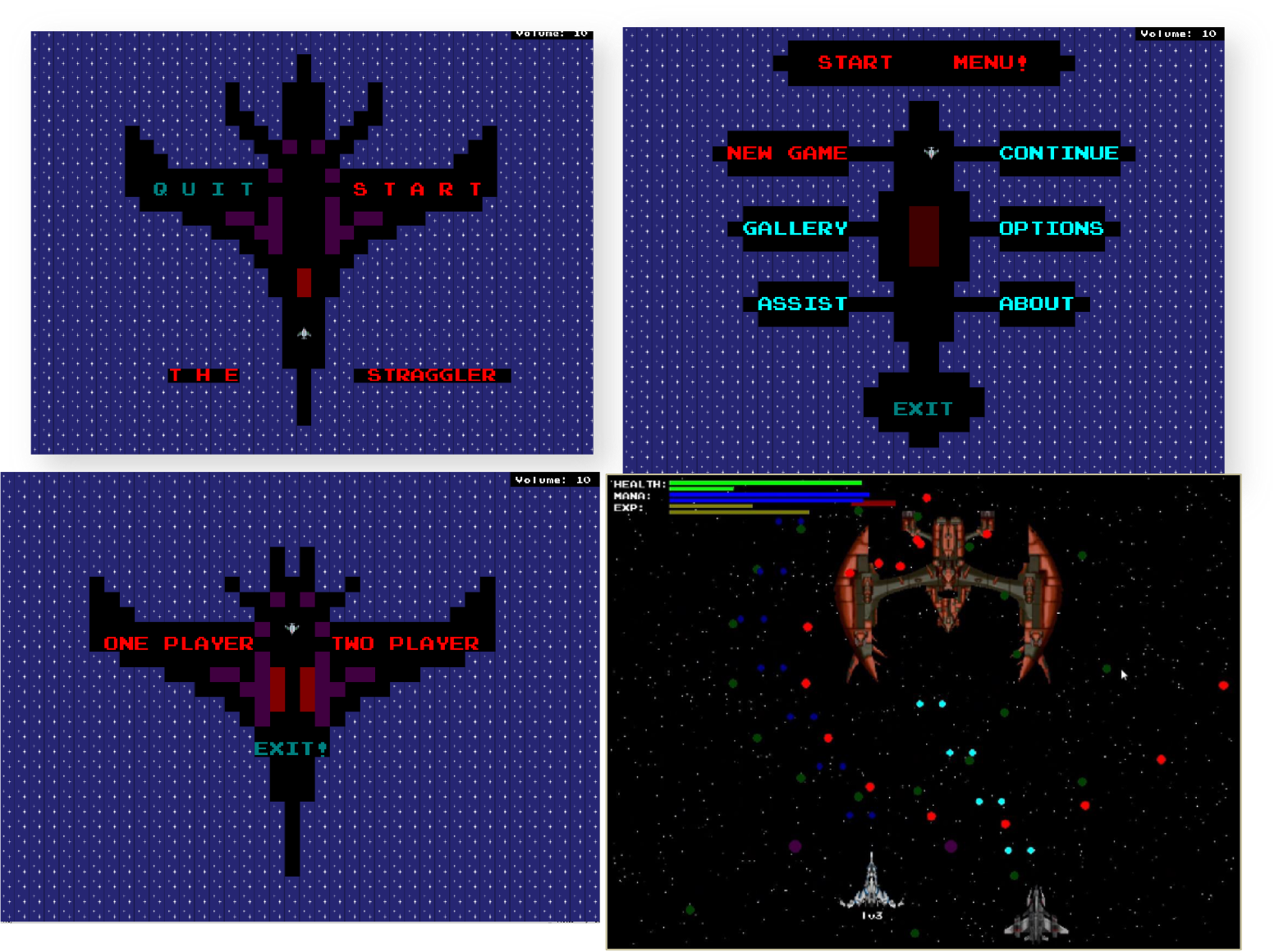

A vertically scrolling shooter video game implemented using C++ in attribution to the classical shooting game, Raiden.

|

|

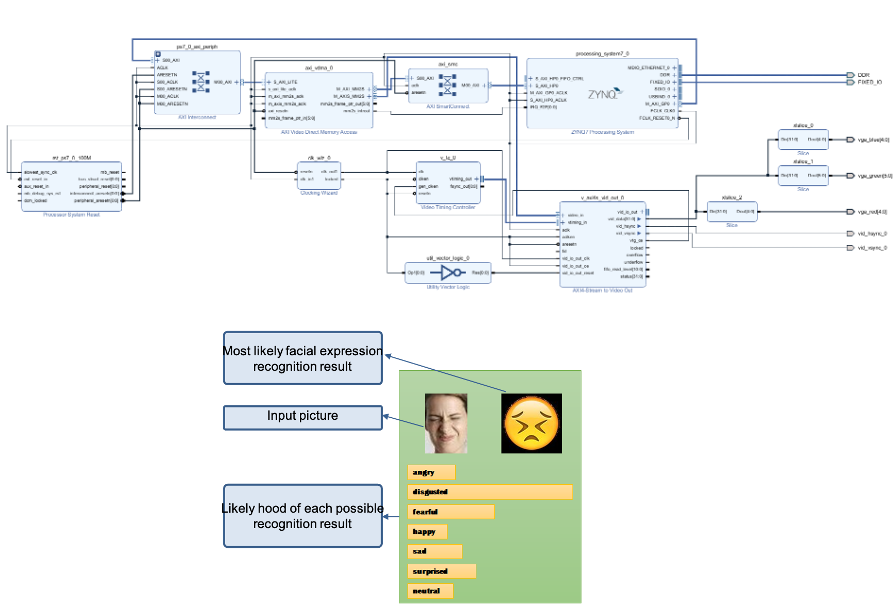

A hardware-software co-design system for facial expression recognition via deep neural networks.

|